-

产品及解决方案

-

服务

-

产品及解决方案

-

服务

-

云原生产品及应用平台

-

云服务

【导读】于基在双线数据线供电(PoD) 架构的Home Bus体系中, 交流阻断 电感负担着分散数据旌旗灯号与直流电源的要害脚色。其机能体现直接决议了通讯收集的不变性及靠得住性,是以怎样精准选型成为体系设计中的主要环节。本文将从工程实践角度出发,具体论述此类非凡运用场景下的电感筛选尺度与体系性评估要领,为构建高机能Home Bus收集提供技能支撑。

择要

于基在双线数据线供电(PoD) 架构的Home Bus体系中, 交流阻断 电感负担着分散数据旌旗灯号与直流电源的要害脚色。其机能体现直接决议了通讯收集的不变性及靠得住性,是以怎样精准选型成为体系设计中的主要环节。本文将从工程实践角度出发,具体论述此类非凡运用场景下的电感筛选尺度与体系性评估要领,为构建高机能Home Bus收集提供技能支撑。

弁言

于工业主动化及楼宇节制体系的通讯收集中,有些节点可能没法接入电源插座,这时候就需要一种既能传输数据、又能提供电力的解决方案,用在毗连多个电路板,好比一个节制器及一个或者多个传感器或者履行器板。假如所有电路板都集中安装于统一机箱中,那末实现上述毗连会很简朴。然而,于典型的节制器-节点收集中,电路板凡是相距数米。跟着节点间间隔的增长及节点数目的增加,布线成本也随之上升,不仅会盘踞解决方案总成本的很年夜一部门,还有会对于体系机能造成显著影响。

一种解决方案是利用四线电缆,一对于线用在数据通讯,另外一对于线用在供电。其长处是解决方案相对于简朴,但错误谬误是电缆成本及重量会增长。更简便的解决方案是利用单对于导线来同时提供数据及电力,这恰是数据线供电(PoD)解决方案的焦点理念。

业界已经经开发出很多差别的PoD解决方案来满意差别类型终极运用的需求。本运用条记会商针对于工业通讯或者楼宇主动化节制体系中常见的专有或者姑且收集的PoD解决方案。这些解决方案有别在基在以太网或者互联网和谈(IP)的解决方案,后者凡是被称为以太网供电(PoE),而较新的单对于以太网(SPE)解决方案则将其称为数据线供电(PoDL)。有关PoE或者PoDL解决方案的信息,请参阅ADI的Chronous产物系列。

数据线供电技能

技能概述

数据线供电(PoD)技能利用双线总线同时向收集上毗连的装备传输电力及数据。电力感性耦合到双线总线上,而数据则是容性耦合。于PoD方案中,每一个节点都需要电感来“阻断”交流数据旌旗灯号,使其不滋扰直流供电。此类电感凡是被称为“交流阻断”电感。双线总线及每一个节点的收发器之间需要电容来将数据旌旗灯号耦合到总线上。此类电容凡是被称为“交流耦合”电容。

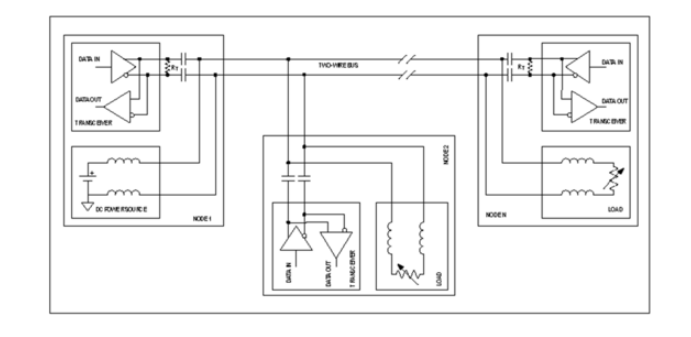

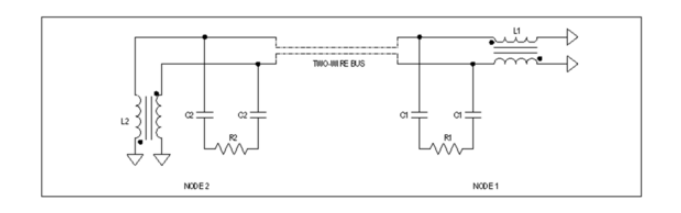

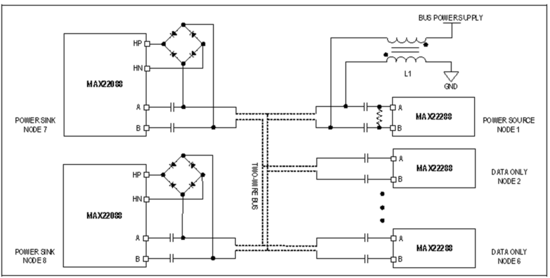

图1显示了利用双线总线的典型多节点PoD收集。这是一个半双工收集,驱动器及吸收器利用一对于路线,数据可以于任一标的目的上传输,但不克不及于两个标的目的同时传输。肆意节点可以于任何给按时间在总线上传输数据,所有其他节点可以吸收数据。“总线”是一种双线电缆,凡是是双绞线或者平行线。此电缆具备特征阻抗(Z0)。于图1中,为了实现抱负的旌旗灯号质量,节点1及节点N处安装了端接电阻(RT = Z0)。典型的多节点PoD收集答应一个节点为总线供电,多个节点可以从总线得到电力。于本例中,节点1为总线供电,其他n-1个节点是负载或者受电节点。

图1.多节点数据线供电(PoD)收集

于很多工业PoD体系中,工程师采用尺度RS-485(或者CAN)收发器构建物理层,并实行一些专有要领经由过程数据线供电。这类收发器已经经很成熟,可以或许于嘈杂的工业情况中稳健地传输数据。体系工程师面对的挑战于在,怎样开发出一种既靠得住稳健,又具有成本效益,同时占用PCB空间极小的电力传输要领。需要留意的是,“交流阻断”电感的尺寸及成本会因收集数据速度及功率容量的差别而有很年夜差异。

RS-485是物理层尺度(OSI模子的第1层),是以它没有固有的数据链路和谈(帧、数据包等)。对于在PoD收集,实行的和谈软件必需包罗某种数据编码方案(如曼彻斯特编码或者8b/10b),以消弭可能呈现的长串0或者1,防止经由过程总线传输电力时因长串0或者1而致使直流不服衡。此类编码的一个错误谬误是需要分外的处置惩罚周期,而且可能造成分外的延迟。

采用PoD架构的体系接口往往具备相对于较低的数据速度(凡是低在5Mbps),可以或许撑持很多节点(64个或者更多),而且撑持长间隔电缆(数百米)。然而,专有通讯和谈虽然于关闭体系中运行优良,但于其他情况中可能会故障装备之间的互操作性。

体系思量因素

于典型场景中,追求PoD解决方案的工程师凡是会存眷如下需求:

• 电力传输(供电节点凡是为24V DC,每一个受电节点为2W至5W)

• 极性无关,简化现场毗连,削减接线过错。

• 数据编码方案应使总线连结直流均衡。

• 只管即便减小电感尺寸以节省成本及PCB空间。

• 机能稳健,包括ESD及EFT等瞬态抗扰度。

供电节点与受电节点

最多见的环境是,体系中一个节点是供电节点(图1中的节点1),而收集上的多个节点是受电节点,由供电节点向受电节点供电。为这些差别类型的节点选择“交流阻断”电感时,需要思量差别的因素。供电节点的电感必需可以或许向整个收集运送全数功率,这凡是要求选用较年夜尺寸的“交流阻断”电感。受电节点的电感到当举行优化,以撑持每一个节点的当地功率需求。

电感尺寸

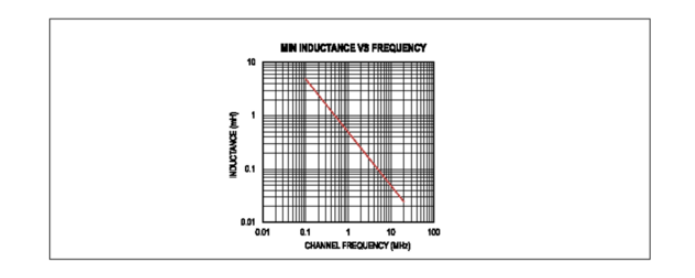

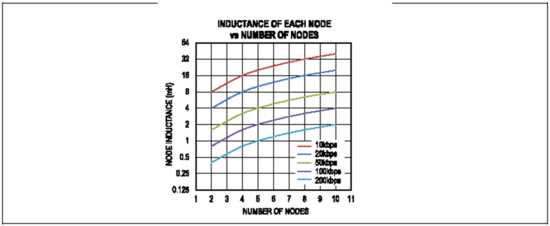

每一个节点上的“交流阻断”电感的作用是将交流数据旌旗灯号与直流电源分隔。PoD体系采用的数据速度相对于较低,这些电感的巨细于毫亨(mH)级别,是以电感体积较年夜,成本较高。图2显示了PoD体系于差别通道数据速度下所需的电感。

图2.每一通道最小电感与频率的瓜葛

当要撑持更高电传播输时,电感尺寸会变患上更年夜,这与当下体系连续缩小的趋向形成冲突,可能成为体系设计的一年夜障碍。

Home Bus体系

Home Bus体系架构概述

Home Bus体系(HBS)是一种风行的PoD解决方案,针对于家庭及楼宇主动化运用举行了优化。ADI公司的Home Bus产物系列撑持实现高效率、高机能的PoD运用。有关Home Bus尺度和其运行道理的更多信息,请参阅Home Bus简介运用条记。

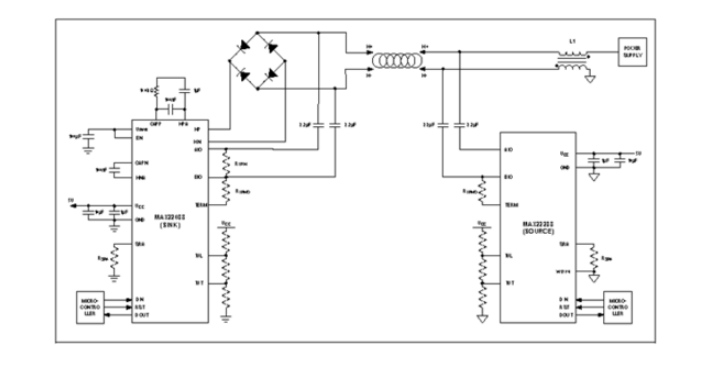

MAX22288收发器专为PoD体系中的供电节点而设计,供电节点需要外部“交流阻断”电感来供电。MAX22088收发器则集成为了“交流阻断”电感,于是可以或许于PoD体系中的受电节点上利用,无需外部“交流阻断”电感。

图3显示了一个双节点Home Bus收集,此中一个节点利用MAX22288,充任供电节点;另外一个节点利用MAX22088,充任受电节点。本运用条记将会商怎样为供电节点选择电感,如图3中的L1所示。请留意,受电节点不需要外部电感,由于MAX22088集成为了有源电感电路以简化体系设计、削减PCB空间并节省成本。

图3.典型的双节点Home Bus体系

总线端接

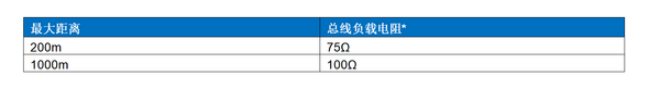

Home Bus尺度划定了差别通讯间隔对于应的总线负载电阻,如表1所示。总线负载电阻是双线总线上维持所有驱动器及吸收器的最小差模电压所必须的最小电阻(最年夜负载)。于现实运用中,负载电阻很年夜水平上由收发器处的端接电阻(RT)决议。为了于总线上得到抱负旌旗灯号质量,端接电阻应与电缆的特征阻抗(Z0)相匹配。

表1.Home Bus负载电阻

*假如利用特征阻抗(Z0)差别的电缆,则应调解端接电阻(RT)以匹配运用中现实电缆的特征阻抗。

MAX22288及MAX22088具备动态电缆端接、可配置吸收器阈值及发送驱动器摆率等特征,可确保得到更好的旌旗灯号质量及矫捷的设计。有关这些特征的具体信息,请参阅MAX22288数据手册。

总线电感

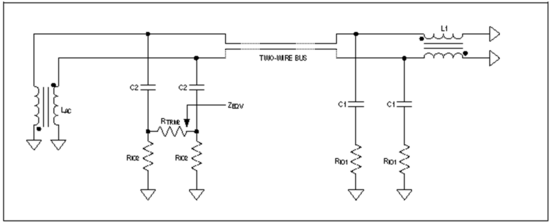

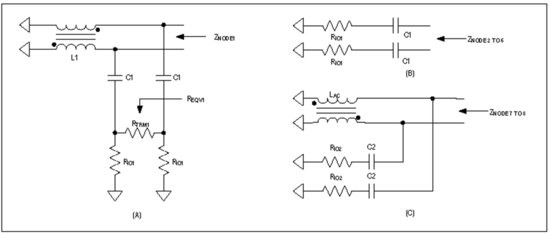

总线的总负载阻抗(ZBUS)是总线看到的端接电阻(RT)、电感(ZL)及电容(ZC)的组合,它必需年夜在表1所示的最小总线负载电阻。图4显示了双节点Home Bus收集的简化等效模子,每一个节点都利用MAX22288,节点1向总线供电,节点2从总线得到电力。

图4.双节点Home Bus收集的简化等效模子

要计较总线总阻抗,应思量总线上的所有元件,根据下式计较ZBUS:

![]()

请留意,L一、C1及R1是节点1的元件值,f是数据速度(单元为赫兹):

●交流阻断电感L1,其阻抗ZL1 = 2π x f x L1

●交流耦合电容C1,其阻抗ZC1 = 1/(2π x f x C1)

●以和端接电阻R1

一样,L二、C2及R2是节点2的元件值。

假定体系设计参数以下:

●端接电阻R1 = R2 = 1kΩ,Home Bus收发器节点为高阻抗

●交流耦合电容C1 = C2 = 22μF

●数据速度为10kbps,或者f = 5kHz

总线的总阻抗(ZBUS)必需至少为100Ω,以满意Home Bus的负载要求。

![]()

于双节点收集中,供给的总功率等在运送的总功率。是以,假定电感L1 = L2,求解ZL:

![]()

于10kpbs数据速度下,所需电感L一、L2为:

![]()

表2显示了典型的双节点Home Bus运用中所需的最小总电感。

表2.所需总线总电感与数据速度的瓜葛

![]()

注:假定ZBUS = 100Ω

假如受电节点利用MAX22088收发器,则可以使用MAX22088集成的“有源电感”向该节点运送电力。此有源电感可调,而且可使用MAX22088数据手册“有源电感”部门所示的公式针对于差别总线前提举行优化。

请留意,因为MAX22088有源电路的实现方式,MAX22088的瞬态相应与尺度差模电感差别。此外,为了撑持动态电缆端接,建议增长电感值,以赔偿毗连动态端接的环境下总线上阻抗的忽然丧失。欲相识更多信息,请参阅MAX22088数据手册中的“动态电缆端接”部门。于有多个毗连节点的更繁杂体系中,电感值会发生变化。针对于差别节点数的多节点配置中的每一个节点,图5提供了所需总线电感的预计值。

图5.多节点Home Bus收集中每一个节点所需的总线电感

于利用长电缆的通讯体系中,电缆两头的端接对于在削减反射及提高旌旗灯号质量很是主要。务必仅端接最远的两个节点;不然,总线负荷会显著增长。对于在更高速率的运用,所需的电感会降低。不外,增长电感不会对于运行孕育发生倒霉影响。

电感选择

选择共同MAX22288供电节点利用的“交流阻断”电感,对于在确保多节点收集靠得住运行至关主要。双线总线需要两个电感,或者者说一对于电感。

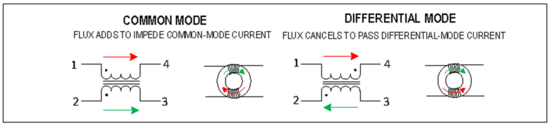

电感对于按照其于电路中的毗连方式,可配置为差别的模式。最多见的两种配置是差模及共模。于差模配置中,电流沿一个标的目的流过一个电感,并沿相反标的目的经由过程另外一个电感返回,从而完成轮回。于共模配置中,电流沿统一标的目的流过两个电感。这些配置有差别的用途。

差模配置会拦阻差模旌旗灯号经由过程,但答应共模旌旗灯号经由过程。对于在差模旌旗灯号,磁通沿相反标的目的经由过程电感,彼此抵消,是以答应差分旌旗灯号经由过程扼流圈。

共模配置于共模旌旗灯号经由过程时变为高阻抗,于差模旌旗灯号经由过程时变为低阻抗。图6显示两个电感摆列成双线共模扼流圈。共模旌旗灯号孕育发生的磁通标的目的不异,是以会拦阻共模旌旗灯号。

图6.共模扼流圈的事情道理

于Home Bus运用中,数据以差分方式经由过程双线总线传输,“交流阻断电感”(现实上是一对于电感)必需配置为对于这些差模数据旌旗灯号出现高阻抗。差模电感会拦阻这些差模数据旌旗灯号;是以,“交流阻断”电感于运行时需要提供差模电感。

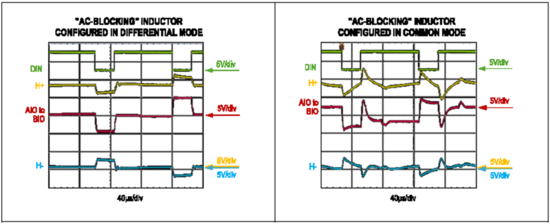

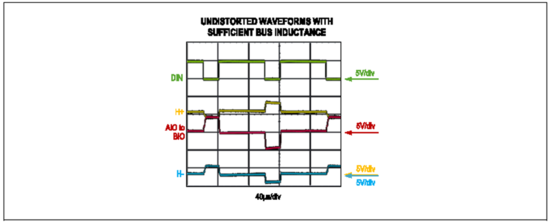

图7显示,当供电节点中的电感对于(图3中L1)配置为差模时,通讯正常(左),但当该电感对于配置为共模时,波形异样(右)。

图7.“交流阻断”电感必需采用差模配置

为Home Bus运用选择差模“交流阻断”电感时,必需满意如下前提:

电感对于的匝数比必需为1:1。这是为了实现均衡操作:数据旌旗灯号标的目的相反,但幅度对于称。

饱及电流必需高在总线上的最年夜事情电流。一旦磁芯饱及,电感就会显著减小。

电感对于至少须提供所需的最小差模电感。请参阅总线电感部门以确定需要多年夜的电感。

电感对于的直流电阻(DCR)必需很是低,凡是应小在10Ω。低DCR可降低直流电传输的电压丧失,晋升收集的总体效率。

建议自谐振频率至少为数据速度的10倍,以确保电感对于于正常前提下以“电感”方式运行。

电感方案

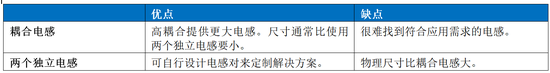

于Home Bus运用中,ADI公司建议利用耦合电感或者两个自力电感作为“交流阻断”电感。

不建议利用变压器或者共模扼流圈作为“交流阻断”电感。

利用耦合电感

建议将差模耦合电感共同Home Bus体系利用。差别供给商对于这种耦合电感有差别的叫法,例如功率电感、扼流圈,甚至变压器。耦合电感是一组经由过程大众磁芯耦合的电感,其耦合系数(k)靠近在1。k越靠近1,磁耦合越好,走漏越少。传统上,耦合电感用在电力电子电路,例如反激式转换器电路。虽然其直流电阻及额定电流可能满意Home Bus运用要求,但电感值凡是小在几百微亨(μH)。要于Home Bus运用中利用耦合电感,须选择具备充足电感值的电感,并留意其测试前提。电感数据手册中的规格凡是是于针对于非Home Bus运用的前提下标定的。是以,建议根据丈量差模电感部门中的步调,于方针事情前提下丈量并标定差模电感。

利用两个自力电感

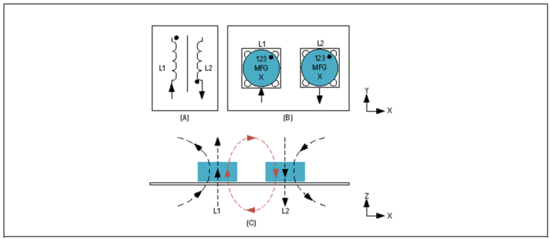

可使用两个零丁的电感于PCB上创立本身的“耦合电感”。采用此方案时请遵照以下两条法则:

法则1:两个电感到尽可能彼此接近放置,以削减磁通走漏。

法则2:以差模配置将其配对于。放置两个零丁电感,使患上于差模旌旗灯号经由过程时,磁通沿不异标的目的孕育发生。

下面的例子利用两个8.3mH线圈电感创立一个电感对于,经由过程它们的磁芯加之此间的空间实现耦合。

图8.两个自力电感的组合和其配置图示:(A)差模毗连,(B)PCB上,(C)差模旌旗灯号经由过程时的磁场

法则1:两个电感到尽可能彼此接近放置,以削减磁通走漏。

当两个电感“耦合”时,电感对于的总电感年夜在L1 + L2(L1及L2的串联组合)。总电感LTOTAL = L1 + L2 + 2M,此中M是L1及L2磁耦合所孕育发生的互感。互感M = k x √(L1xL2),此中k是介在0及1之间的耦合系数。k=1暗示磁通漏泄为零,L1及L2之间100%磁耦合。图8(C)中的红线暗示两个电感之间的磁耦合;两个电感位置越近,耦合越抱负,走漏越小,是以互感M越年夜。

耦合系数k = 1时,如图8(A)所示配置的两个8.3mH电感的终极差模电感为L1 + L2 + 2k x √(L1 x L2) = 33.2mH。现实上,耦合系数k始终小在1。当这两个电感相距1妹妹时,测患上的差模电感为25.8mH。电感减小是由磁通走漏酿成的。互感M = 0.5 x (25.8mH - 8.3mH x 2) = 4.6mH,注解耦合系数k = M/√(L1 x L2) = 4.6mH/8.3mH = 0.55。

当这两个电感相距1cm时,终极差模电感进一步减小,实测值为19.3mH。耦合系数降至0.33。

当这两个电感相距10cm时,测患上的差模电感为16.6mH,与两个自力电感串联毗连且无任何磁耦合的环境不异。这象征着磁耦合太弱,没法孕育发生任何成心义的互感。

法则2:以差模配置将其配对于。放置两个零丁电感,使患上于差模旌旗灯号经由过程时,磁通沿不异标的目的孕育发生。

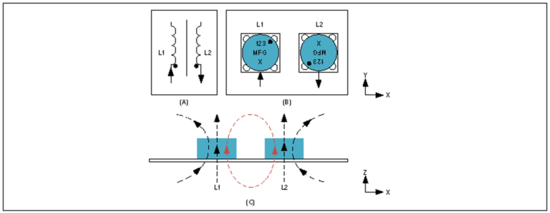

当耦合对于采用共模配置时,两个电感的磁通于差模旌旗灯号经由过程时,沿不异标的目的孕育发生并彼此抵消,如图9所示。总电感LTOTAL减小,小在L1及L2的串联组合。

图9.(A)共模毗连,(B)PCB上,(C)差模旌旗灯号经由过程时的磁场

当两个电感采用差模配置(如图8(B)所示)且相距1cm时,测患上的差模电感为20.3mH,年夜在两个自力电感的串联组合16.6mH。磁通相加,使患上终极耦合电感更年夜。

当两个电感采用共模配置(如图9(B)所示)且相距1cm时,测患上的差模电感为14.7mH,小在16.6mH。磁通彼此抵消,使患上终极耦合的差模电感减小。

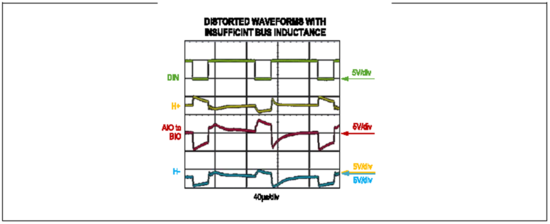

于图10及图11中,两个Home Bus节点以50kbps的速度举行通讯,利用两个自力电感创立“交流阻断”电感对于。从表2可知,于50kbps数据速度下,所需的总线总电感为0.8mH。图10显示,当利用两个390μH电感来实现780μH的总电感(小在所需的最小总线电感)时,吸收器波形发生掉真。电感对于负载200mA电流,这进一步降低了总线上的总有用电感。图11显示,当电感对于由两个3.9mH电感组成以实现年夜在所需最小值的总线电感时,不异事情前提下的总线波形洁净无掉真。

图10.50kbps总线波形,利用两个390µH自力电感作为“交流阻断”电感对于

图11.50kbps总线波形,利用两个3.9mH自力电感作为“交流阻断”电感对于

利用变压器

电力变压器用在于低级侧及次级侧之间升压或者降压。于Home Bus运用中利用变压器时,应留意如下要求:

确保匝数比为1:1。年夜大都变压器的匝数比凡是不是1:1。低级侧及次级侧凡是具备差别的交流电压。

丈量差模电感,由于数据手册中往往不会给出线圈电感。

变压器凡是尺寸重大,需要盘踞巨年夜的空间。

利用共模扼流圈

共模扼流圈用在滤除了共模噪声。年夜大都共模扼流圈不合适Home Bus运用,缘故原由以下:

●差模电感比共模电感小患上多。

●共模扼流圈的额定电流相对于较小,其典型事情频率凡是远高在Home Bus运用利用的数据速度。

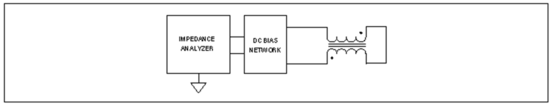

丈量差模电感

年夜大都电感的数据手册未提供Home Bus运用所用数据速度及偏置电流前提下的差模电感信息。凡是,鉴定所选电感对于的最简朴要领是利用LCR表测定其特征。于运用的数据速度及偏置电流下丈量差模电感及相位时,应留意如下几点:

●抱负电感具备+90°相位,象征着其电漂泊后在其电压90°。

●当电感磁芯饱及时,电感值会迅速降落。数据手册中有时会给出滚降率。

●每一个电感都有一个自谐振频率,该值凡是随直流偏置电流而变化。

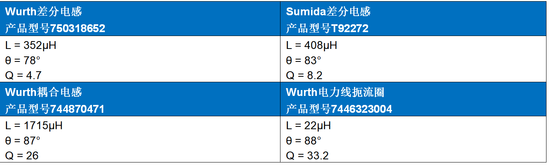

利用LCR表是标定所选电感的最简朴要领。图12显示了利用LCR表丈量差模电感的典型设置。表3展示了于试验室中利用Instek LCR-6300仪表举行丈量的四个例子,并列出了它们于200kbps数据速度及200mA负载电流的Home Bus运用中的机能。

图12.利用LCR表丈量差模电感

表3.利用LCR表举行特征阐发及波形丈量

按照表2,200kbps前提下所需的总线最小总电感为200μH。Wurth共模电力线扼流圈(产物型号7446323004)没法提供所需的最小差模电感,是以总线波形发生掉真。

设计示例

示例1:57.6kbps的双节点收集

思量一个以57.6kbps数据速度运行的双节点Home Bus收集,如图3所示。图13为简化的等效模子。供电节点经由过程“交流阻断”电感L1向总线供给100mA电流,而MAX22088经由过程其集成的“有源电感”从总线获取电力。于此示例中,元件针对于57.6kbps数据速度举行了优化,选择Wurth Electronics, Inc. 的100mH耦合电感(产物型号750318652)作为“交流阻断”电感L1。

图13.双节点收集等效模子

为了确定此耦合电感可否用在该运用,计较总线上的总阻抗ZBUS = ZL1 || (ZC1+ RIO1) || (ZC1 + RIO1) || ZLAC || (ZC2 + REQV + ZC2),此中:

L1 = 138mH(20kHz、100mA偏置电流前提下,来自基准特征测试)

LAC = 22.4mH(利用MAX22088数据手册中的公式)

静态端接电阻RTRM2 = 1kΩ

MAX22288 AIO/BIO输入阻抗RIO1 = 30kΩ(典型值)

MAX22088 AIO/BIO输入阻抗RIO2 = 10kΩ(典型值)

REQV = 952Ω,由下式患上出:1/REQV = 1/(2 x RIO2) + 1/RTRM2

耦合电容 = 2.2μF

数据速度 = 57.6kbps,或者f0 = 28.8kHz

以是,

ZL1 = 2π x f0 x L1 = 25kΩ

ZLAC = 2π x f0 x LAC = 4kΩ

ZC1 = ZC2 = 1/(2π x f0 x 2.2μF) = 2.5Ω

ZC1 + RIO1 = 30kΩ

ZC2 + REQV + ZC2 = 957Ω

是以,ZBUS = ZL1 || (ZC1+RIO1) || (ZC1 + RIO1) || ZLAC || (ZC2 + REQV + ZC2) = 25kΩ || 30kΩ || 30kΩ|| 4kΩ || 957Ω = 713Ω,年夜在所需的最小总线端接电阻100Ω。

MAX22088及MAX22888评估套件均利用了该Wurth耦合电感,它撑持57.6kbps的Home Bus运用。

示例2:200kbps的8节点收集

于此示例中,思量一个以200kbps速度运行的8节点Home Bus体系,如图14所示。L1是供电节点中的“交流阻断”电感,为总线提供共计250mA的电流。咱们需要确定是否可以或许利用Wurth Electronics, Inc.的耦合电感(产物型号744851102)。

图14.简化的8节点Home Bus体系

总线上的总阻抗ZBUS = ZNODE1 || ZNODE2 || ZNODE3 || ZNODE4 || ZNODE5 ||ZNODE6 || ZNODE7 || ZNODE8,此中:

ZNODE1是节点1(供电节点)的总阻抗。

ZNODE2至ZNODE6是节点2至6(纯数据节点)的总阻抗。

ZNODE7及ZNODE8是节点7及8(受电节点)的总阻抗。

图15.(A)节点1(供电节点)、(B)节点2至6(纯数据节点)及(C)节点7至8(受电节点)的等效电路

思量供电节点和其等效电路,如图15(A)所示,ZNODE1 = ZL1 || (ZC1 + REQV1 + ZC1),此中:

L1 = 358μH(100kHz、250mA偏置电流前提下,来自基准特征测试)

静态端接电阻RTRM1 = 1kΩ

MAX22288 AIO/BIO输入阻抗RIO1 = 30kΩ(典型值)

REQV1 = 983.6Ω,由下式患上出:1/REQV1 = 1/(2*RIO1) + 1/RTRM1

耦合电容 = 1μF

数据速度 = 200kbps,或者f0 = 100kHz

以是,

ZL1 = 2π x f0 x L1 = 225Ω

ZC1 = 1/(2π x f0 x 1μF) = 1.6Ω

ZC1 + REQV1 + ZC1 = 987Ω

是以,ZNODE1 = 225Ω || 987Ω = 183Ω。

思量纯数据节点和其等效电路,如图15(B)所示,ZNODE2-6 = (ZC1 + RIO1) || (ZC1 + RIO1),此中:

MAX22288 AIO/BIO输入阻抗RIO1 = 30kΩ(典型值)

ZC1 = 1/(2π x f0 x 1μF) = 1.6Ω

是以,ZNODE2-6 = (30kΩ + 1.6Ω) || (30kΩ + 1.6Ω) = 15kΩ。

思量受电节点和其等效电路,如图15(C)所示,ZNODE7-8 = ZLAC || (ZC2 + RIO2) || (ZC2 + RIO2),此中:

LAC7 = 35mH(50mA负载电流下,利用MAX22088数据手册中的公式)

LAC8 = 16mH(200mA负载电流下,利用MAX22088数据手册中的公式)

MAX22088 AIO/BIO输入阻抗RIO1 = 10kΩ(典型值)

以是,

ZLAC7 = 2π x f0 x LAC7 = 22kΩ

ZLAC8 = 2π x f0 x LAC8 = 10kΩ

ZC2 = 1/(2π x f0 x 1μF) = 1.6Ω

是以,ZNODE7 = 22kΩ || (10kΩ + 1.6Ω) || (10kΩ + 1.6Ω) = 4kΩ,ZNODE8 = 10kΩ || (10kΩ + 1.6Ω) || (10kΩ + 1.6Ω) = 3.3kΩ。

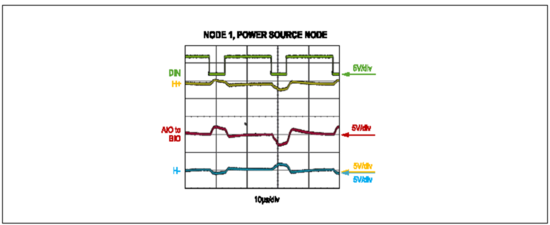

总线上的总阻抗ZBUS = ZNODE1 || ZNODE2 || ZNODE3 || ZNODE4 || ZNODE5 || ZNODE6 || ZNODE7 || ZNODE8 = 183Ω || (15kΩ / 5) || 4kΩ || 3.3kΩ = 157Ω,年夜在所需的最小总线端接电阻100Ω。图16显示了节点1(供电节点)处的总线波形。

图16.节点1(供电节点)处的总线波形

结语

本运用条记论述了为Home Bus体系选择适合“交流阻断”电感的尺度。建议利用“耦合电感”或者配置为“电感对于”的两个自力电感。务必按照现实运用前提,采用本运用条记中会商的尺度及要领,于实验台上确定所选的“交流阻断”电感是否及格。

本运用条记还有提供了示例及基准丈量成果,以帮忙读者为Home Bus运用选择适合的电感。

参考文献

MAX22088数据手册及MAX22088评估套件

MAX22288数据手册及MAX22288评估套件

Home Bus简介,Home Bus简介 | ADI公司

电感供给商:

• Wurth Electronics, Inc.,www.we-online.com

• Sumida Corporation,https://www.sumida.com

©2024 Analog Devices, Inc.保留所有权力。所有牌号及注册牌号均属各自所有人所有。One Analog Way, Wilmington, MA 01887-2356, U.S.A.

保举浏览:

工程师必读:步进机电选型避坑指南,精准匹配运用需求

深耕中国市场:艾迈斯欧司朗摸索者年夜会展示 于中国、为中国 战略

解密将来安全:后量子暗码技能怎样重塑数字生态

数据大水下的算力突围:英特尔以生态之力破局AI范围化

离别线缆杂乱!HDMI怎样用单根线重塑音视频传输

-米兰·(milan)