-

产品及解决方案

-

服务

-

产品及解决方案

-

服务

-

云原生产品及应用平台

-

云服务

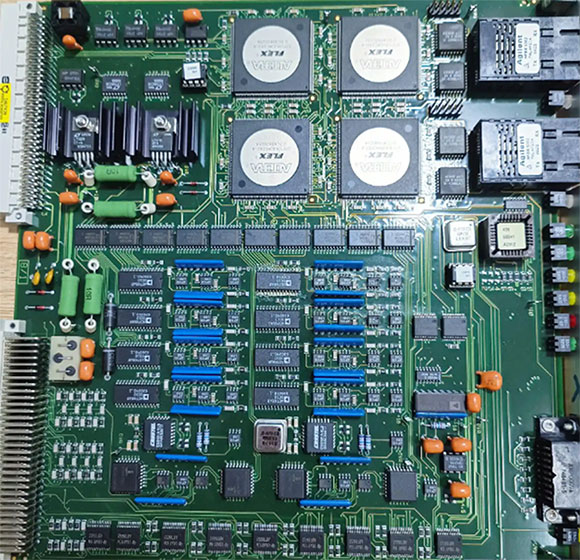

【导读】当数据速度冲破56Gbps时,电源分配收集(PDN)的微小阻抗颠簸足以瘫痪整块高速板卡。本文将展现从电容选型到叠层架构的体系级去耦方案,经由过程重构电流路径与阻抗节制模子,完全解决电压塌陷与电磁滋扰的行业恶疾。

1、电容选型认知革命:打破容量堆砌迷思

传统方案的物理陷阱初期工程师习气并联多规格电容(10nF至1μF)试图笼罩全频段需求,实则堕入三重困局:

谐振点散射:差别容值电容的本征谐振频率分离,于1GHz频段形成锯齿状阻抗峰

寄生电感叠加:多个电容的等效串联电感(ESL)彼此耦合,高频阻抗飙升逾2Ω

噪声反升悖论:某FPGA板卡添加100nF电容后,实测电源纹波反而恶化15%

科学选型新范式▶封装同质化原则同一采用0402/0201小型贴片封装,将单电容ESL压缩至0.2nH内▶谐振频点聚焦法基在芯片瞬态电流需求(ΔI/Δt)计较方针阻抗曲线,精选谐振点匹配的电容族群▶三级防护圈结构以BGA芯片为中央修筑梯度防地:• 焦点圈(1妹妹内):10颗同批次0.1μF X7R电容形成高频樊篱• 缓冲圈(5妹妹层):4.7μF钽电容组平抑中频纹波• 输入防地:22μF电解电容接收低频脉动

2、电流路径拓扑学:最小回流环节制术经典掉败案例解析某8层通讯板卡因结构掉误激发灾害性后果:• DDR4旌旗灯号地弹噪声达120mV(超JEDEC尺度2.4倍)• 电磁辐射于3.5GHz频点超标8dB,被迫从头设计

三维优化要领论 垂直向叠层革命抱负架构遵照 旌旗灯号层→地平面→电源平面→旌旗灯号层 的黄金规则:• 电源/地平面间距≤0.2妹妹,形整天然漫衍式电容(15nF/cm²)• 介质质料介电常数Dk 4.2时,储能密度晋升3倍

程度向布线铁律• 高速旌旗灯号正下方必需保流连续地平面• 电源过孔与引脚间距≤1.5倍板厚(按捺涡流损耗)• 严禁跨支解区布线(防止孕育发生>30mA回流电流)

工程实证效果于112G光模块违板实行后:• 旌旗灯号过冲幅度降低72%• 电源阻抗曲线全频段平展化(0.8Ω@100MHz-10GHz)

3、PDN阻抗驯服术:从频域到物理的映照三阶协同阻抗模子低频域(<100MHz)依靠电解电容组不变基础电压中频域(100M-1GHz)由MLCC阵列抚平电流纹波高频域(>1GHz)依附平面电容接收纳秒级突变

反谐振点消弭实战

经由过程频域扫描定位阻抗凹坑频率

部署特定ESR电容抵消谐振峰

某GPU主板实行后谐振振幅衰减12dB

叠层电容倍增效该当采用2盎司铜厚电源层时:• 平面距离0.1妹妹可以使阻抗降低40%• 介质损耗角正切值Df<0.02时,高频不变性晋升3倍

4、EDA协同设计流:Altium实战指南四阶闭环设计法 层叠预配置阶段利用Stackup Manager构建≤4mil介质层对于称布局 场效应仿真阶段输入电容ESL/ESR参数天生三维阻抗云图 热区预判阶段PDN Analyzer主动标志电流密度>30A/妹妹²高危区 动态验证阶段加载IBIS模子模仿毫秒级负载突变

企业级效能对于比经验驱动型设计凡是需要6次以上迭代,首版妨碍率高达43%采用EDA协同流将迭代压缩至2次内,妨碍率降至9%如下

结语:电源完备性的体系级破壁PDN设计素质是能量传输的周详跳舞——当0.2妹妹的平面临距化身缓冲带,当0402电容阵列组成高频卫士,56Gbps数据大水方能平安飞跃。这不仅是电子工程的巅峰武艺,更是数字文明算力基石的保存规则。

保举浏览:

SiC怎样重塑工业充电设计?断绝DC-DC拓扑选型指南

德州仪器电源路径充电技能解析:怎样实现电池寿命与体系机能的共赢?

力芯微ET75016激光驱动芯片:从头界说TOF 3D传感精度与效率

多维科技TMR13Nx磁开关芯片:从头界说智能笔360°无死角叫醒体验

-米兰·(milan)

版权所有2016-2025 米兰(milan)数码集团股份有限公司,保留一切权利。