-

产品及解决方案

-

服务

-

产品及解决方案

-

服务

-

云原生产品及应用平台

-

云服务

【导读】当电子装备的机能寻求愈发严苛,特别是游戏等高负载场景下的极致体验,对于电源转换技能提出了史无前例的挑战:既要磅礴动力(300W级),又需超高效率与紧凑形态。硅基功率器件日渐涉及物理天花板,这差遣财产眼光转向潜力巨年夜的氮化镓(GaN)。安森美iGaN技能作为高效能电源的前锋代表,怎样赋能300W游戏适配器的设计?本文将剖析其焦点上风,并深切切磋要害设计要素如电源治理、旁路电容等实现高效的要害点。

GaN技能上风

GaN作为一种宽禁带半导体(Wide Bandgap Semiconductor),其质料特征自然地优在硅,于多个要害指标上具有显著上风。于不异输出功率的前提下,GaN可于 MHz 等级的开关频率下事情,能显著缩小磁性元件(如变压器与电感)与滤波电容的体积,实现更高的功率密度与更小的体系尺寸。

GaN元件具有较小的输入与输出电容,同时无反向恢复电流,能有用降低死区时间损耗(Dead Time Loss)与反向恢复损耗(Reverse Recovery Loss),使其于高频开关下仍维持高效率。虽然GaN的单元面积成本高在硅,但其更低的 RDS(on)使总体效率更佳,并能削减散热器面积与体系散热需求。

虽然GaN自己具有卓着机能,但其驱动与节制的难度较高。纯真采用分立式GaN所带来的设计挑战不容轻忽,尤其是于高频驱动、PCB 布线、EMI 节制与靠得住性设计方面,难度远高在传统硅 MOSFET。为相识决上述问题,整合型GaN(Integrated GaN,简称iGaN)技能应运而生。

安森美iGaN概述

本文将先容安森美(onsemi)所推出的iGaN产物,为读者于元件选择与体系设计上提供现实参考。同时,本文针对于PCB Layout 实操技巧与参考设计准则,协助设计者现实运用并优化体系效能。文章末了,提供300W高效能游戏适配器的参考设计以和试验数据。

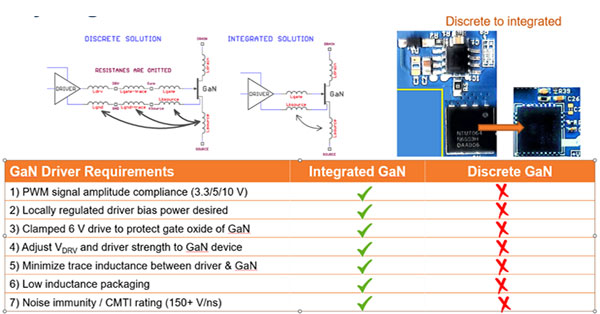

安森美将 e-mode GaN与栅极驱动器(Gate Driver)整合在单一封装中。如许的整合年夜幅削减了 PCB 上的布线长度与相干的寄生参数,使患上GaN开关可以更快速、更不变地运作。如图1所示,安森美的产物带来的上风包括:

· PWM旌旗灯号幅度合规性:可以或许兼容多种PWM旌旗灯号幅度,包括3.3V、5V及10V。这使患上集成GaN技能于差别的运用场景中具备更高的矫捷性及顺应性。而分立GaN没法满意多种PWM旌旗灯号幅度的需求。

· 6V钳位驱动掩护GaN栅极氧化层:具备6V钳位驱动功效,可以或许有用掩护GaN栅极氧化层,避免其遭到太高电压的侵害。分立GaN技能则缺少这一掩护办法,可能会致使GaN栅极氧化层于高电压情况下遭到侵害。

· 调治VDRV及驱动强度以驱动GaN速率:可以按照需求调治驱动强度,以顺应差别的运用要求。这使患上iGaN技能于差别的运用场景中具备更高的矫捷性及顺应性。

· 最小化驱动器及GaN之间的路线电感:可以或许最小化驱动器及GaN之间的路线电感,这有助在提高体系的机能及靠得住性。分立GaN技能则没法有用削减路线电感,可能会致使体系机能降落。

· 噪音免疫性/CMTI评级(150+ V/ns):具备较高的噪音免疫性及CMTI评级(150+ V/ns),这有助在提高体系的不变性及靠得住性。分立GaN技能则没法提供这一功效,可能会致使体系于高噪音情况下呈现不不变的环境。

图1 安森美iGaN的上风

安森美作为业界领先的 iGaN 技能供给商,其 NCP5892x系列涵盖650V/ 50mohm, 78mohm以和150mohm 规模,广泛运用在快充电源、工业电源、办事器电源模组等范畴。

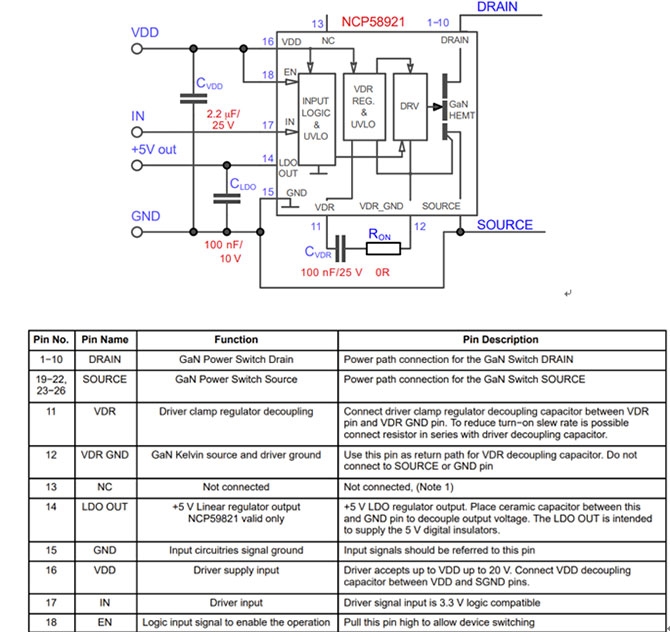

图2以NCP58921为例,出现功效框图及引脚申明。该产物将高机能高频驱动器及 650 V、50 mΩ 氮化镓 (GaN)整合于一个开关布局中。硅驱动器及 GaN HEMT 功率开关的强盛组合,比拟分立式 GaN,机能更卓着。 同时,TQFN26 8 x 8 妹妹封装降低了电路及封装寄生效应,同时实现了更紧凑的设计。

图2 NCP58921的功效框图及引脚申明

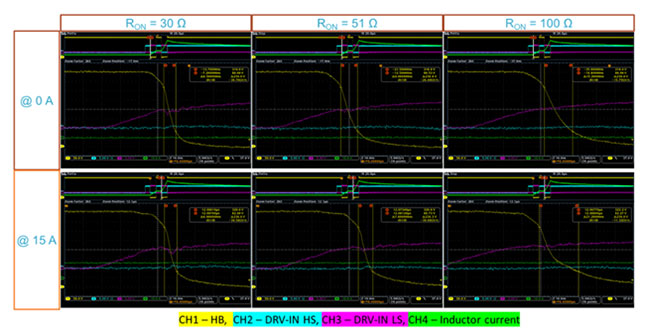

另外一方面,利用者会于给定的运用及前提下查抄元件的电压应力或者是体系EMI特征。缘故原由是PCB 结构寄生电容以和电感寄生电容及电源回路杂散电感会影响开关切换的体现。NCP58921 可透过串联 RON电阻及 VDR 去耦 CVDR 电容来调解开启压摆率 (dv/dt)。

建议的 VDR 去耦电容为多层陶瓷电容器 (MLCC) X7R 材质。 CVDR电容为 100 nF,额定电压高在 25 V,可提供更好的热/电压不变性。务必添加串联电阻 (RON),以便设定turn on slew rate并举行运用调试。建议的肇始 RON值为 33 Ω。 RON电阻值取决在运用要乞降事情频率,但 100 Ω 应被视为最年夜值。图3是调解差别的RON值,体现出差别的dv/dt。

图3 iGaN透过调解RON孕育发生差别的 dv/dt

iGaN虽已经年夜幅降低传统GaN设计于驱动与匹配上的坚苦,但优良的 PCB layout仍是阐扬其高速、高效率特征的要害。特别于高电压、高频率、高功率密度运用中,即便微小的布线掉误,也可能激发 EMI、切换尖峰、震荡甚至元件毁坏。

接下来,将以现实设计为导向,慢慢申明 iGaN 的 PCB 布线原则,涵盖要害元件摆放、高频回路设计以和接地处置惩罚。

VDD, LDO旁路电容

iGaN于高速驱动驱动历程,于栅极电容的短暂充电时期需要更高的电流。此电源电流透过内部调治器从 VDD 解偶电容 CVDD 提供,该电容用在解耦 VDD 电源电压。 CVDD 必需直接毗连于 VDD 及 GND 接脚之间。 CVDD 电容应为至少 1 uF的陶瓷电容,并尽可能接近电源引脚,以便滤除了高频操作下所有的突波。

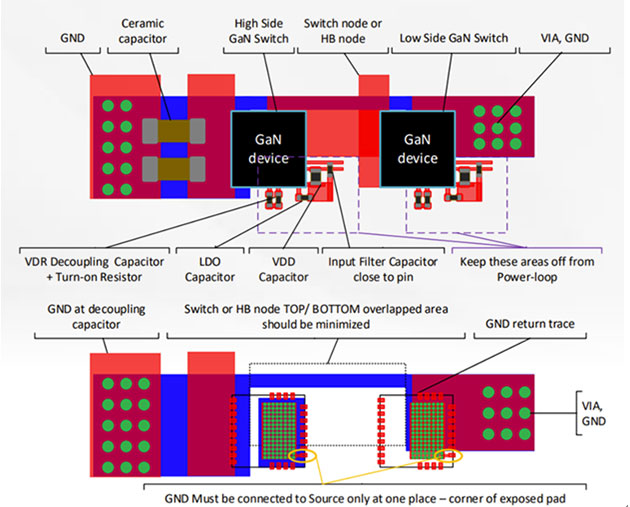

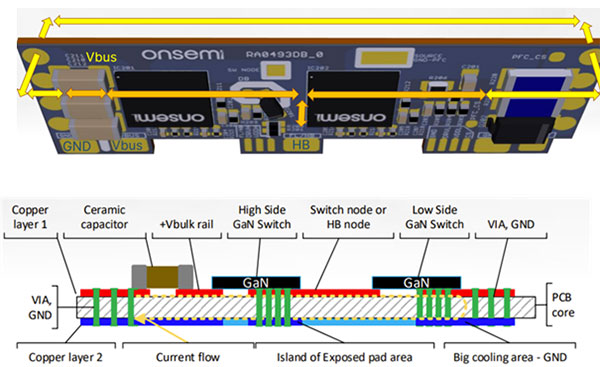

LDO OUT 是通用稳压器的输出,用在为 5 V 数字断绝器或者断绝栅极驱动器供电。此稳压器需要于 LDO OUT 及 GND 引脚之间毗连陶瓷电容,以解耦输出电压。建议电容值为 100 nF,其质料应为不变性优良的 X7R。图4为典型的半桥电路PCB结构以和元件位置,可看到CVDD位在VDD的引脚四周,LDO OUT的引脚与GND之间也有陶瓷电容。

图4 半桥架构下Layout结构

削减寄生电感

假如功率回路中的寄生电感太年夜,搭配iGaN极高的电流变化率 di/dt,轻易孕育发生尖峰电压,甚至致使毁坏。同时,这也会孕育发生年夜量辐射 EMI。如图5所示,标示了Vbus、HB、GND 以和阁下的 bypass 陶瓷电容。咱们可以看到,从Vbus → iGaN →Switch Node →iGaN,再经由 Via 返回 GND,这整条就是高功率电流回路。为了削减寄生电感,于PCB结构时,把iGaN与旁路电容(MLCC)放于相互紧邻位置,削减回路的长度。同时,利用宽铜面,并于下一层有完备 GND 作为返回路径,可形成电场与磁场的抵销。上层与内层中间的板厚越薄越好,有助在形成耦合电感来等效削减整个路径上的寄生电感。

图5 半桥架构下的高功率电流路径

削减Switch Node 寄生电容

iGaN器件具备很是低的输出电容,而且以高dv/dt快速切换,从而孕育发生很是低的开关损耗。为了连结这类低开关损耗,必需最小化添加到(switch node)开枢纽关头点的分外电容。按照电容的公式,C=0.0886⋅εr⋅A/h

这里:

εr:是质料的介电常数,FR4 材质约为 4.5

A:是 Switch Node 与其他平面(如 GND 或者Heatsink)的堆叠面积

h:是这两个导体之间的间隔(凡是为板厚、Dielectric)

简朴来讲,最小化开枢纽关头点平面与其他电源及地平面的堆叠,总体形成的寄生电容 C 也会随着降落。此外,亦可以经由过程如下指南来最小化开枢纽关头点的寄生电容:

1. 将功率电感器尽可能接近iGaN器件。

2. 功率电感器必需利用单层绕组组织,以最小化绕组内电容。

3. 假如单层电感器不成行,思量于主电感器及iGaN器件之间放置一个小电感器,以有用屏蔽GaN器件免受分外电容的影响。

4. 假如利用反面散热器,利用起码的开枢纽关头点铜笼罩面积于底层铜层上,以改善热散热。

-米兰·(milan)